Online Catalogue - Exhibitor News

In semiconductor fabrication environments, static electricity is invisible and intangible — yet its destructive power is measured in nanoseconds.

Direct breakdown:

The human body typically cannot sense electrostatic discharge (ESD) below 3,000 V. However, for chips with line widths of only a few nanometers, an accidental discharge of just a few dozen volts can puncture the gate oxide layer, rendering an entire wafer scrap.

Potential Induced Damage (PID):

Even more concerning is low-voltage discharge. The chip may not fail immediately, but internal “hidden damage” remains, leading to early product failure and becoming a reliability time bomb.

Particle attraction:

Charged surfaces act like vacuum cleaners, attracting microscopic airborne particles. In a Class 10 cleanroom, a single 0.1 μm particle landing in a photolithography area can destroy the entire wafer pattern.

Therefore, from wafer fabrication to packaging, testing, and transportation, antistatic materials are essential. However, different processes and contact conditions require different levels of static control — which brings us to the question of resistivity selection.

The Antistatic Material Family: Four Resistivity Ranges, Four “Roles”

The core parameter of antistatic materials is surface resistivity (unit: Ω). It is not “the lower, the better,” but rather “the better the match, the better the performance.” These four categories can be understood as four different “roles” in a semiconductor facility.

10¹⁰–10¹² Ω Antistatic PEEK: Engineered for “Critical Scenarios”

In semiconductor manufacturing, certain applications impose seemingly contradictory requirements:

The material must prevent static, yet remain electrically insulating; withstand high temperatures, yet maintain cleanliness; retain the mechanical strength of PEEK, while providing antistatic functionality.

This is precisely where 10¹⁰–10¹² Ω antistatic PEEK finds its purpose. It does not replace conductive or dissipative materials — instead, it fills the “gap” between insulation and conductivity.

1. Suppressing Charge Generation — Not Relying on Grounding

The core logic of dissipative materials (10⁶–10⁹ Ω) is “rapid discharge,” which requires a reliable grounding path. However, in certain precision structures, grounding may be impractical or may interfere with electrical design.

Materials in the 10¹⁰–10¹² Ω range follow a different approach:

-

Charge suppression: Material modification reduces the likelihood of triboelectric charge generation.

-

Slow neutralization: If charges are generated, they dissipate gradually through micro-conduction pathways or neutralize via ambient ions.

-

Applicable scenarios: Ideal for applications where grounding is inconvenient, or where both electrical insulation and antistatic performance are required.

2. Preserving PEEK’s “Flagship Properties” Without Compromise

Conductive PEEK (<10⁵ Ω) typically requires high carbon filler loading. While conductivity improves, mechanical properties may decline (e.g., increased brittleness).

In contrast, 10¹⁰–10¹² Ω antistatic PEEK achieves static control through intrinsic or low-additive technologies, preserving PEEK’s inherent strengths, including:

-

High temperature resistance (continuous use up to 260 °C)

-

Excellent mechanical strength (capable of replacing metal in certain applications)

-

Chemical resistance (withstands strong acids and alkalis during cleaning processes)

-

Low ionic extractables (protecting wafer purity)

3. Bridging the Gap Between “Insulative” and “Dissipative”

-

Standard PEEK (Insulator >10¹² Ω): Suitable for high-insulation requirements, but may accumulate static under high-speed friction.

-

Dissipative materials (10⁶–10⁹ Ω): Suitable for grounded applications requiring rapid discharge.

-

Antistatic PEEK (10¹⁰–10¹² Ω): Positioned in between — capable of gradually releasing static to prevent accumulation while maintaining insulating properties and not interfering with circuit design.

It is not “better,” but “different” — providing a professional solution for applications that require PEEK performance, antistatic functionality, and electrical insulation simultaneously.

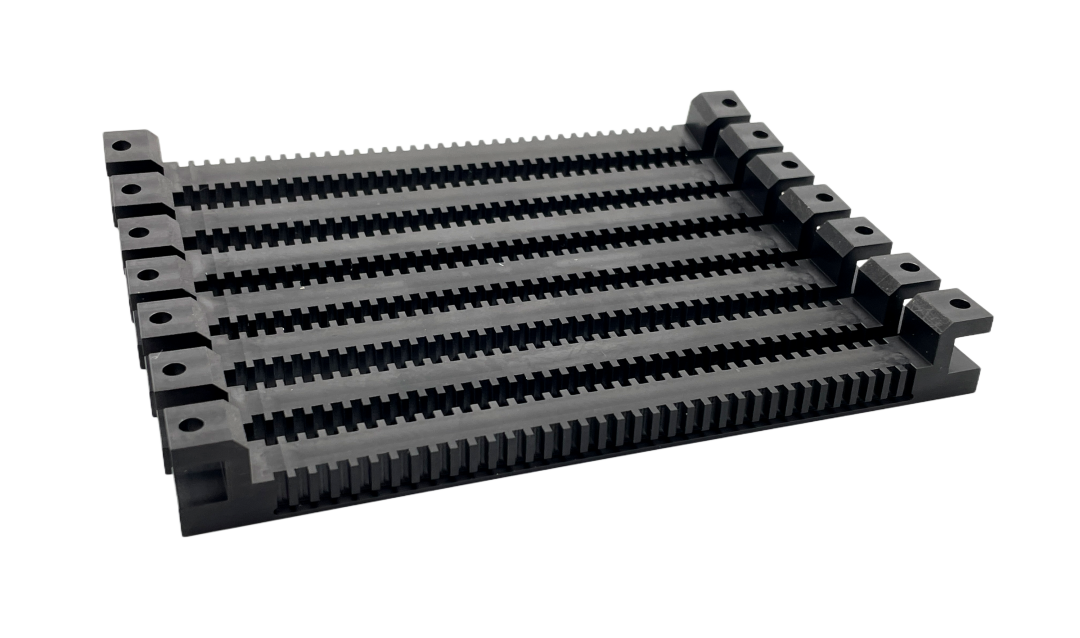

Typical Engineering Applications of JUTAIPEEK® ESD 10#12

-

Semiconductor IC test sockets

-

Wafer handling components (waffle pads, trays)

-

Probe station components

-

Insulating structural supports

JUTAI’s Next-Generation Antistatic Technology

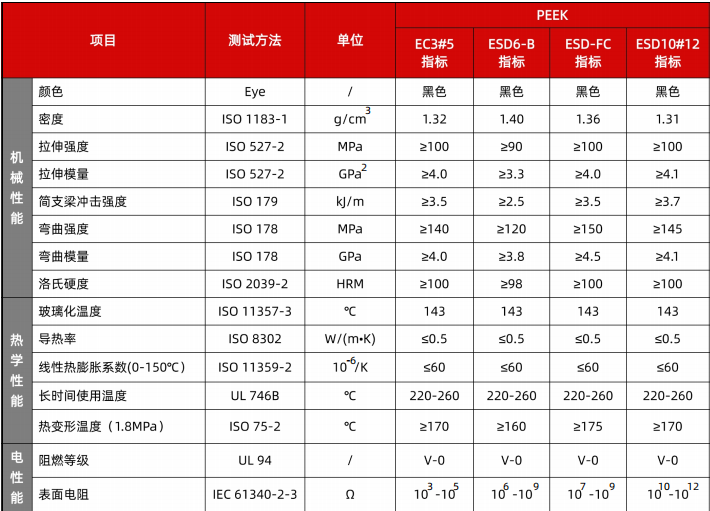

Product Property Table:

Exhibitor Profile

苏州聚泰新材料有限公司

2928

The content of this System has been provided by the exhibitors and Messe Muenchen Shanghai Co., Ltd. (hereinafter referred to as “MM-SH”) will not assume any liability for the correctness, completeness and up-to-date status of the content.

This System includes links to external websites of third parties, MM-SH have no influence on the contents of these websites. In all cases, the respective site provider or operator shall be responsible for the content of the sites linked. MM-SH do not bear any legal liability therefrom.

In particular, MM-SH reserves the right to make changes or extensions to the information provided without prior notification. Decisions based on the information provided on or via this System are for your own account and risk. MM-SH shall not be liable for any direct or indirect damages caused by use of information provided on or via this System.

MM-SH do not bear any legal liability for any loss arising from any direct or indirect use of contents of this System, including without limitation the losses resulted from error, omission or virus, etc.

The information, photos and logos, etc. in relation to the exhibitors in this System are all provided by exhibitors (in case the exhibitor does not provide exhibitor logo, the show logo will be displayed) and any download or use of the content for commercial purpose without authorization is prohibited. If you have any objection, please contact MM-SH.

沪公网安备31011502016746号

沪公网安备31011502016746号